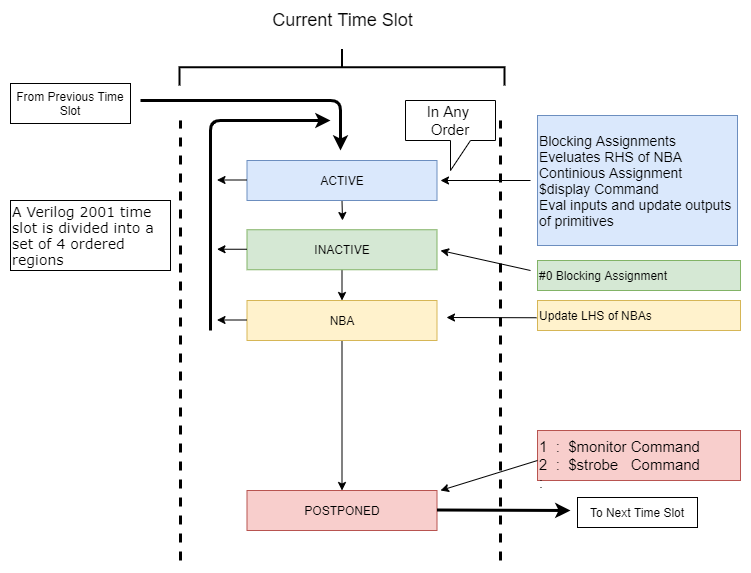

Verilog IEEE 1364- 2001 divided the Verilog event regions into four ordered regions.

1 : Active Events

2 : Inactive Events

3 : Non Blocking Assignment Update Events

4 : monitor or strobe events

Below image explains in which region which statement will execute.

Now question comes why it is important?

see below examples to understand it.

Example 1: Continious assignment and $display which executes in active region.

Value of temp = 101

Example 2: Here at 0 simulation time two different values assign to same variable using blocking and non-blocking assignment.

When we simulate this code result of $display and $strobe is different. but why?

because they execute in different regions.

Blocking assignment(temp=4'b0011) and $display execute in active region so, $display print 3 as output, and another thing is in blocking assignment RHS evaluated and assign at same time.

In Non-blocking assignment RHS evaluated in active region and assign in NBA region and this is the reason $display print 3. And once value assign to LHS then $strobe and $monitor system task executes. first $strobe and then $monitor.

Output:

[$display] Value of temp = 3

[$monitor] value of temp = 12

[$strobe] value of temp = 12

Example 3: Race condition blocking assignment.

always@(posedge clk)

a=b;

always@(posedge clk)

b=a;Here two process runs in parallel , intent is to swap two variables but since blocking assignment evaluate and assign at same time output is not predictable.

Example 4: Swaping using Non blocking assignment

always@(posedge clk)

a<=b;

always@(posedge clk)

b<=a;

Here it will swap value correctly, because non blocking assignment evaluate RHS in active region and assign to LHS in NBA region.

There are some guidelines where to use blocking and non-blocking assignment , where to use $display and $strobe.

Guideline 1 : Sequential logic - use nonblocking assignment

Guideline 2 : Latches - use nonblocking assignment

Guideline 3 : Combinational logic in procedural block - use blocking assignment

Guideline 4 : Mixed sequential and combinational logic in same always block - use nonblocking assignment.

Guideline 5 : Do not mix blocking and nonblocking assignment in same always block

Guideline 6 : use $strobe to display values that have been assigned using nonblocking assignment

Guideline 7 : Do not use #0 in procedural block

Thank You , for reading. Have a nice day😀😀.